HL-LHC : L’IN2P3 fait ses premiers pas dans les détecteurs 4D

Une équipe d’ingénieurs en micro-électronique a développé et testé deux générateurs d’horloge de très haute précision. Ces composants serviront à battre la mesure dans les détecteurs du futur collisionneur haute luminosité du CERN (HL-LHC) afin de chronométrer à 2 picosecondes près le moindre événement qui s’y produira. Cette 4e dimension « temporelle » qui vient enrichir les données, améliorera la précision et la qualité des mesures tout en diminuant le flot de données à traiter. Ces travaux ont été menés par trois laboratoires du CNRS1 dont le Laboratoire de physique des 2 infinis - Irène Joliot-Curie (IJCLAB - CNRS / Université Paris-Saclay / Université Paris-Cité) à Orsay.

- 1IJCLAB, IP2I et LPC

Dans le futur LHC Haute Luminosité (HL-LHC) le nombre de collisions proton-proton simultanées doit passer de 40 actuellement au LHC, à près de 200. L’empilement des signaux va devenir tel que de nouvelles stratégies d’enregistrement doivent être développées afin d’aider à démêler un à un chaque jaillissement de particule dans les détecteurs. Un axe majeur de développement poursuivi par plusieurs expériences de physique (Atlas@HGTD, CMS@HGCAL, ECAL2@LHCb, TOF-PET...) consiste à effectuer un découpage temporel de chaque prise de vue des détecteurs grâce à un traitement électronique ultra fin. En d’autres termes, il s’agit d’étiqueter précisément l’instant d’arrivée de milliers de signaux dans une même prise de vue. De cette manière, les physiciens et physiciennes pourront reconstituer le film de la formation de l’image finale et relier plus facilement les différentes traces les unes aux autres.

Horloge de grande précision

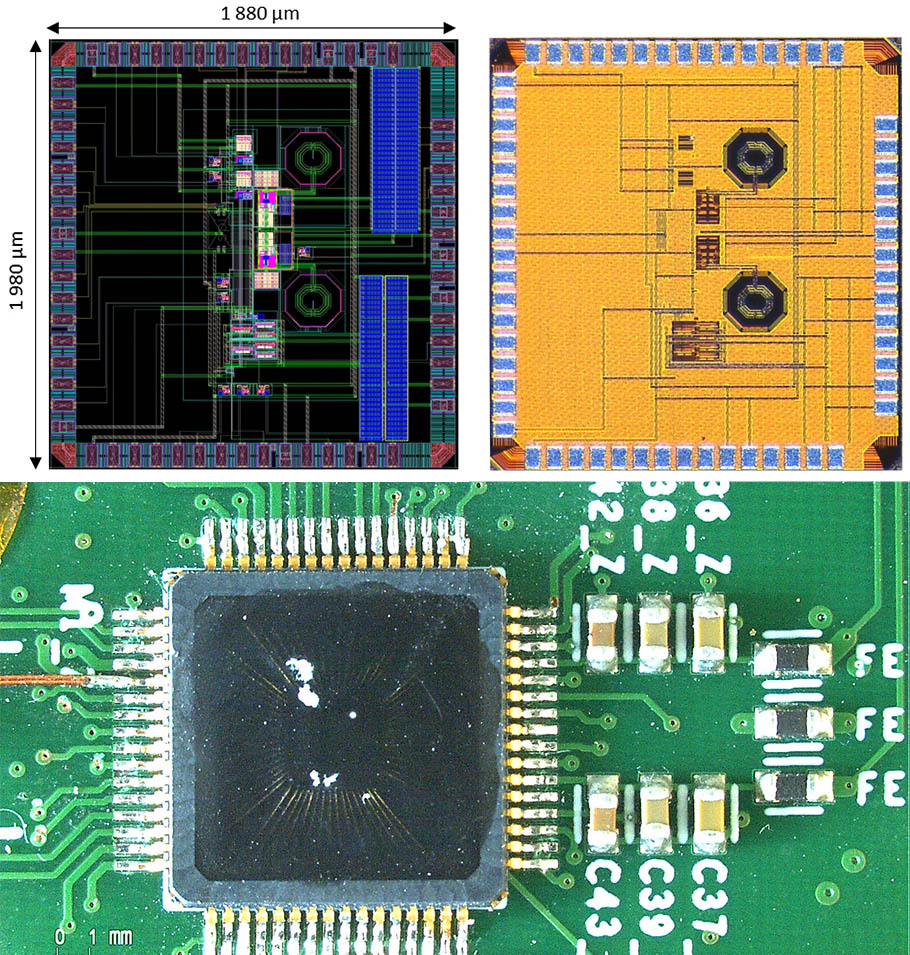

Cette stratégie a été explorée par une équipe de micro-électroniciens de trois laboratoires de l’institut (IP2I, IJCLab et LPC) dans le cadre du projet de R&T Lojic130 du CNRS porté par le Pôle MicRhAu. Leur travail a débouché sur le développement et la mise au point de deux composants, appelés « boucles à verrouillage de phase » (PLL ou « Phase Locked Loop »), qui battent la mesure à 2,56 GHz avec une précision remarquable. Les tests et mesures qui ont été conduits, ont montré que chaque battement avait une précision de 2 picosecondes, soit un « jitter absolu » de 2ps rms dans le jargon de l’électronique. Cette exactitude sonne comme une très bonne nouvelle pour les physiciens, car sans elle, l’étiquetage en temps n’aurait pas apporté de véritable plus-value à leurs analyses. « C’était une bonne surprise d’atteindre cette précision, explique l’équipe d’ingénieurs impliqués dans le test, d’autant que nous avons travaillé sur de la technologie silicium très classique TSMC 130 nm qui nous limite en fréquence comparé aux technologies à 65 nm ou 28 nm. »

Deux composants testés

Deux PLLs ont été conçues : la première est basée sur un oscillateur harmonique LC (association d’un condensateur et d’une bobine) et la seconde sur un oscillateur en anneaux (oscillateur auto asservi qui oscille en permanence entre un état haut et bas). « Dans les deux cas, nous avons mesuré un jitter absolu de 2ps assurent les concepteurs. Par contre les deux architectures ont des avantages et inconvénients qu’il faudra arbitrer en fonction du cahier des charges des détecteurs. L’oscillateur LC, par exemple, est gourmand en surface de silicium, tandis que l’oscillateur en anneau est plutôt gourmand en énergie. » Dans le cadre du projet de R&T Fastime, cette brique de base a encore été optimisée et vient d’être couplée à un circuit de mesure de temps, qui utilise les battements de la PLL pour « chronométrer » des événements. Là aussi les résultats sont prometteurs car en simulation, le jitter obtenu est inférieur à la picoseconde. Le circuit sera gravé prochainement pour être testé sur une carte électronique en début d’année prochaine.

Le projet Lojic130 a fait l’objet d’une publication en mai 2022. Il a permis d’acquérir un savoir-faire important pour concevoir les prochaines générations d’Asics dans le domaine de la mesure de temps. Un transfert vers la technologie TSMC 65 nm est prévu dans le cadre d’un R&T2 pour le futur calorimètre électromagnétique de LHCb.

- 2Ce projet, porté par IJCLAB, vise à fournir un étiquetage en temps des événements, calculé à partir d’un échantillonnage du signal à base de mémoires analogiques.